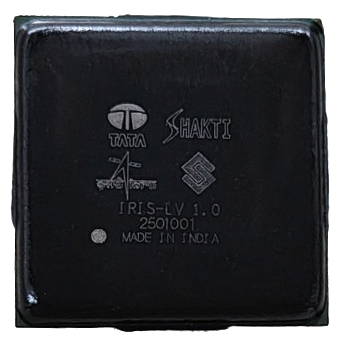

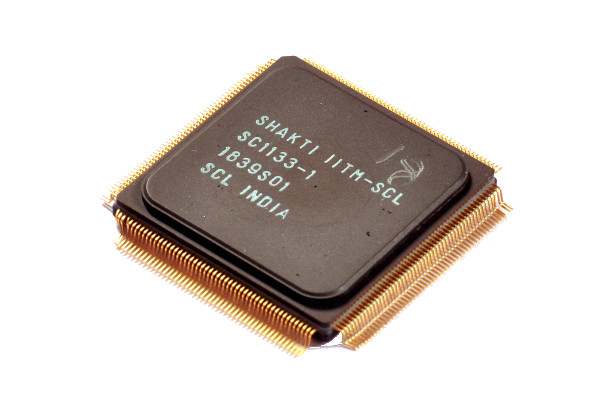

Code Name: RISECREEK (Test-Chip)

Core Design Details

- Design Team: IIT Madras

- Entire design is open-source.

- SHAKTI Family: C-Class

- Performance: 1.68 DMIPs/MHz

- ISA: RV64IMAFD

- User Spec: 2.2

- Privilege Spec: 1.10

- Supervisor Support: sv39

- 5-stage in-order core.

- AXI-4 Fabric - Crossbar topology

- 16KB I-Cache and 16KB D-Cache - 4-way set associative

- Separate I-TLB and D-TLB - fully associative

- Simple 2-state branch predictor

- Sequential low overhead IEEE-754 compliant Single and Double Precision FPUs

- 6-entry Return Address Stack

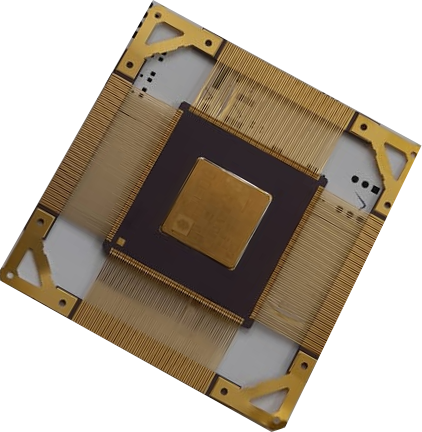

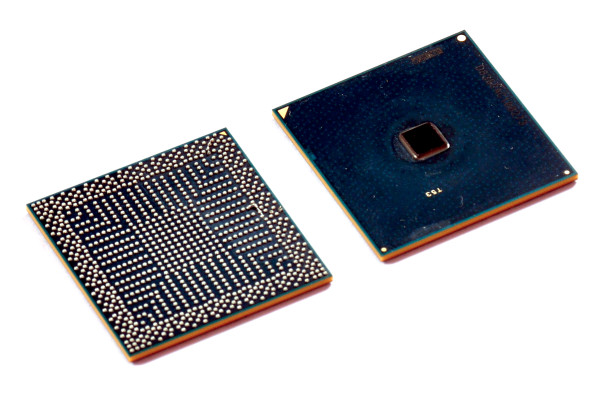

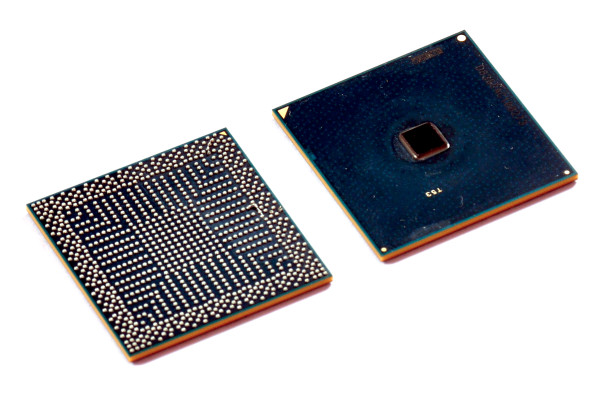

Chip details

- Manufacturer: Intel

- Date of Shipment: July 2018

- Technology Node: 22nm FinFet

- Die Size: 4 x 4 mm2

- Functional IOs: 324

- Packaging: BGA

- Core Voltage: 0.75V

- IO Voltage: 1.8V

Physical Design Details

- Physical Design Team: HCL Technologies

- Max Closure Frequency: 350 MHz

- SoC Gate Count: 370K

- Core Gate Count: 140K

- On Chip PLL

Peripherals and Devices

- Design Team: IIT Madras

- All devices are open-source

- 1x 64-bit SDRAM from open-cores

- 2x QSPI

- 2x I2C

- 1x Tightly Coupled Memory - 128KB

- 1x JTAG for Debug compatible with 0.13 spec.

- 32x GPIOs

- 1x DMA compatible with AXI-4

- 1x Simple UART - rx/tx signals only

- 1x 16550 based UART

Software Support

- Software Team: IIT Madras

- RISC-V Linux has been ported and booted on the chip.

- FreeRTOS has also been ported.

- Paranoia and other Tests have also been successfully ported on the chip

Board Details

- Board Design Team: HCL Technologies+IIT Madras

- Board Manufacturer: Ohm CAD systems