# **SHAKTI C-Class SoC Verification**

Lavanya Jagadeeswaran

Project Manager | SHAKTI Lab | RISE Group

#### **This Session**

2

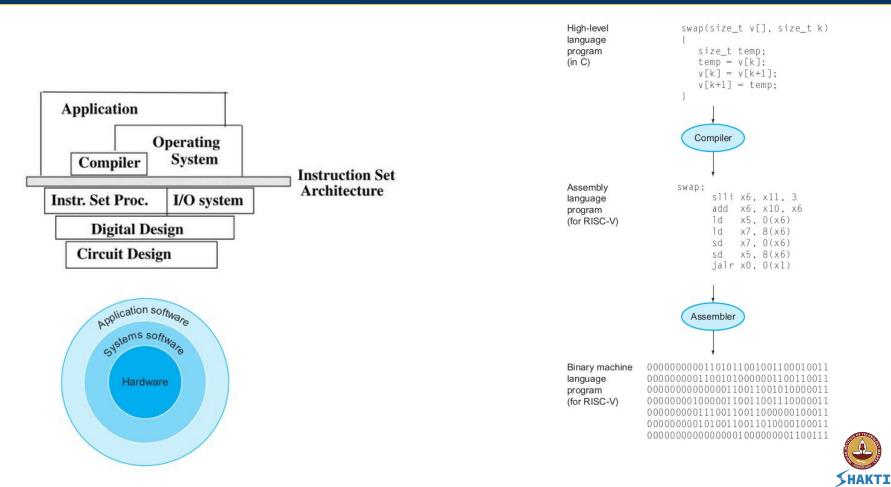

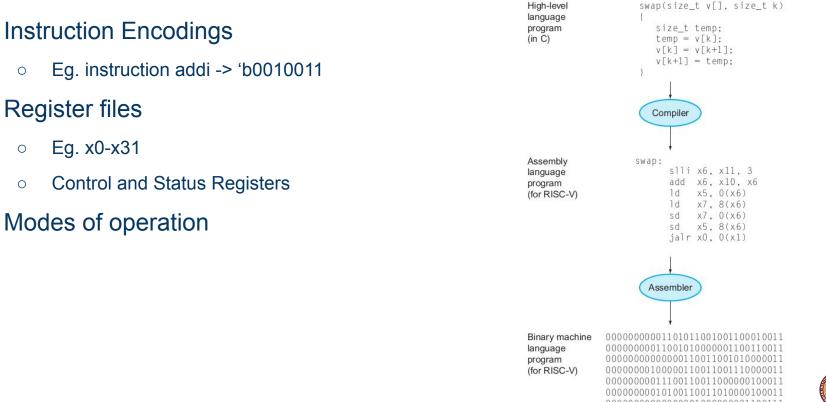

# What does any ISA Specification define

Ο

0

Ο

# **RISC-V** Implementation & Why we need it ?

- Numerous processor implementations based on RISC-V

- IITM's SHAKTI Class of processors, CDAC's VEGA, SiFive's Rocket, Freedom, OpenHW's CV32E40P, CVA6 and many more

- The specification defined in terms of hardware design is known as its implementation

- Isolation of architecture from implementation

- In order to bring out a bug free implementation, verification engineers are expected understand the architecture and basic underlying principles governing the implementation

- Pipelining: Hazards, Memory hierarchy, Branch predictions, In order, Out-of-order processors

#### How to verify them ?

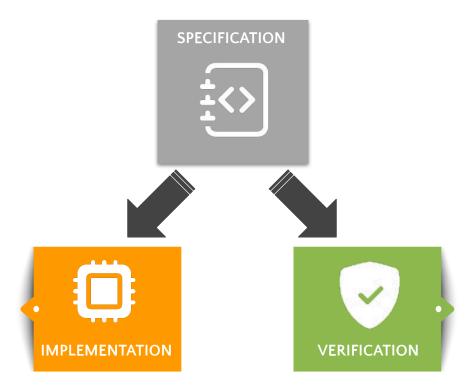

# Verification - Catch bugs!

- Demonstrates functional correctness

- Based on the same specification

- Bug escapes to silicon is costly

- More than 50% of resource (time, money, manpower) spent on verification

#### **SHAKTI Verification**

- SHAKTI Verification is based on open-source tools and the framework is maintained commonly for various classes of RISC-V cores like C-Class, E-Class, I-Class maximizing reuse.

- Comprehensive suites of directed and random assembly tests are simulated on the Bluespec generated verilog design using Verilator

- Processor verification incorporates ISA level state checking at every instruction execution along with end of test memory check.

- Self-checking frameworks are developed to aid simulation and FPGA level verification

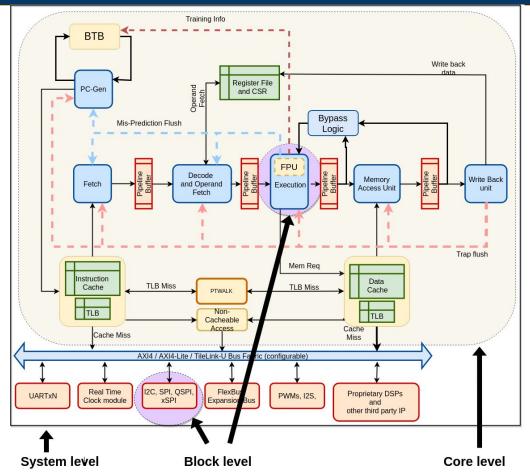

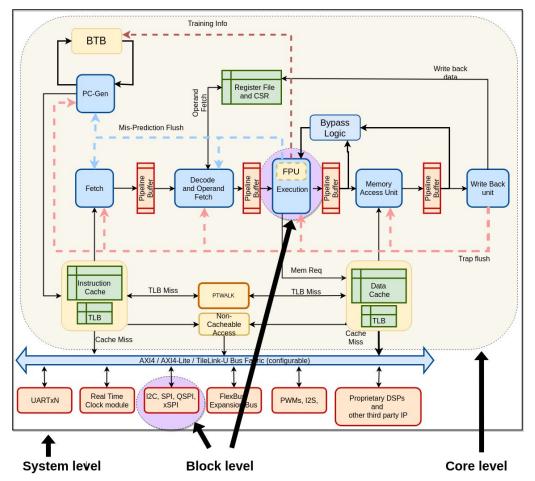

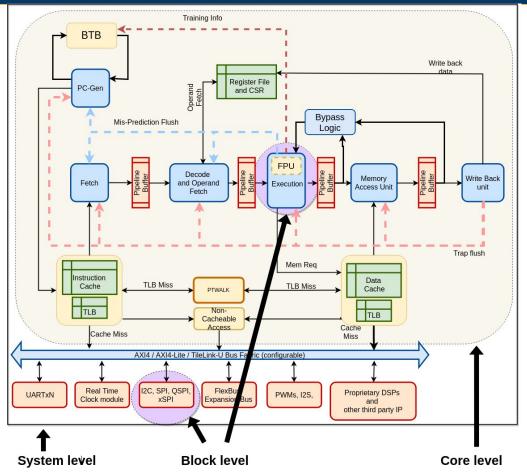

# **SHAKTI Verification Levels**

#### Block level

- UVM methodology

- Interaction with DUT using CoCoTb libraries

- Core level

- RISC-V core verification

- Framework generating and simulating directed/random tests

- System level

- Simulation & FPGA based verification

8

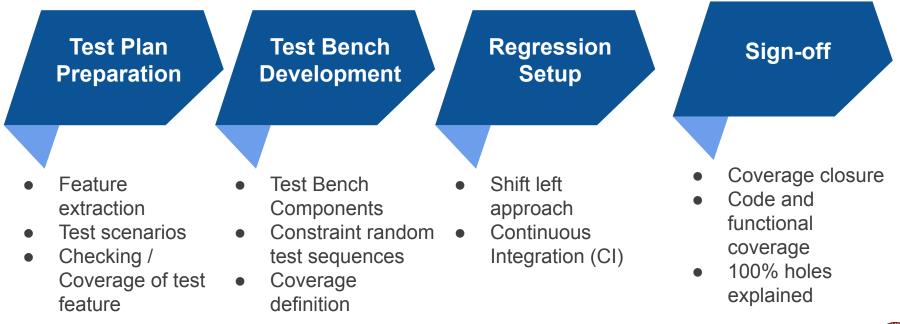

# **Generic Verification Methodology**

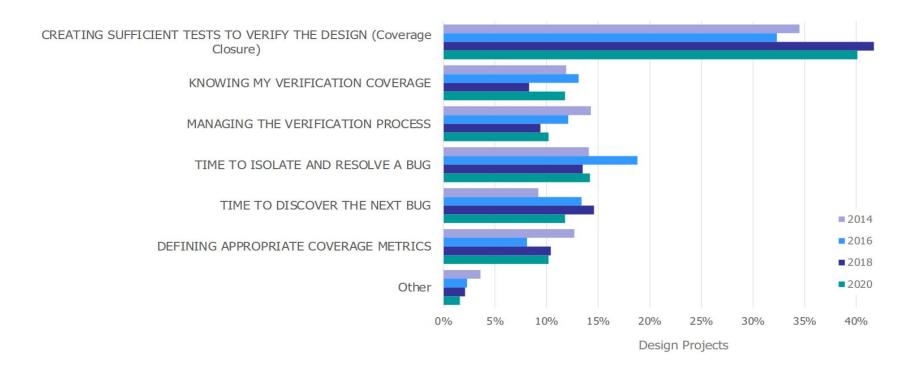

# **Verification Challenges**

Ref: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

# Why Verification is Important ?!

| Bug                                                                  | Year | Loss                                                                      |

|----------------------------------------------------------------------|------|---------------------------------------------------------------------------|

| Intel's FDIV Bug                                                     | 1994 | <b>\$475 million</b> for replacements ~ \$752 million in 2020.            |

| Intel's Cougar Point<br>chipset problem                              | 2011 | \$300 million in lost sales and <b>\$700</b><br><b>million</b> in repairs |

| Spectre and Meltdown<br>Secutiry Flaws Affect<br>Intel, ARM, and AMD | 2018 | ~ \$18 billion                                                            |

Refs:

https://en.wikipedia.org/wiki/Pentium\_FDIV\_bug

https://www.anandtech.com/show/4143/the-source-of-intels-cougar-point-sata-bug

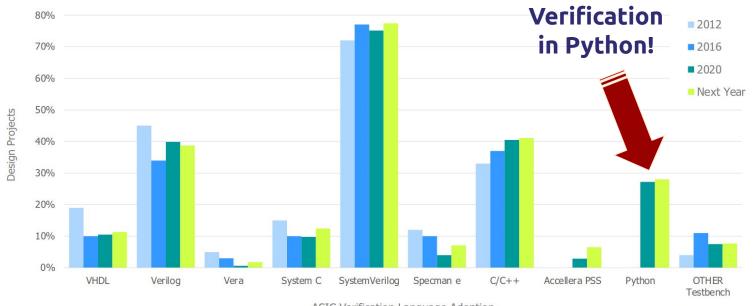

# **Emerging Trends**

ASIC Verification Language Adoption

\*\* Multiple answers possible

Ref: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

### **Verification Components - Test Development**

- For RISC-V core verification purposes, self checking assembly tests are used

- riscv-tests

- riscv-arch-tests

- Implementation specific tests

- RISC-V Random test generation

- Shakti's AAPG

- RISCV-Torture

- Google's RISCV-DV

- MicroTesk

- Force-RISCV

Test Suite Development & Generation

RISC-V Toolchain for Test Compilation

> Reference Model Development

Test Bench for Processor State Comparison

> Regression & Coverage Collection

#### **Verification Components - Test Compilation (SW)**

Test Suite Development & Generation

Reference Model Development

Test Bench for Processor State Comparison

> Regression & Coverage Collectior

- riscv-gnu-toolchain

- For custom extensions, toolchain support has to be added

#### **Verification Components - Reference Model**

Test Suite Development & Generation

RISC-V Toolchain for Test Compilation

#### Reference Model Development

Test Bench for Processor State Comparison

> Regression & Coverage Collectior

- Spike, the Instruction Set Simulator is used as the reference model

- Alternate commercial support: riscvOVPSim

#### **Verification Components - Test Bench**

Test Suite Development & Generation

RISC-V Toolchain for Test Compilation

> Reference Model Development

Test Bench for Processor State Comparison

Regression & Coverage Collection

- Shakti's C-Class employs log based processor state comparison and UVM based verification environment

- Processor State:

- XPR, FPR and CSR. mem on loads/stores

#### **Verification Components - Regression**

Test Suite Development & Generation

RISC-V Toolchain for Test Compilation

> Reference Model Development

Test Bench for Processor State Comparison

Regression & Coverage Collection

- Shift-Left Approach

- Design and verification starts in parallel

- Verification support incrementally added based on the design feature addition

- Design merge triggers smoke regression

- Nightly regression using Continuous

Integration

# **SHAKTI SoC Verification Summary**

19

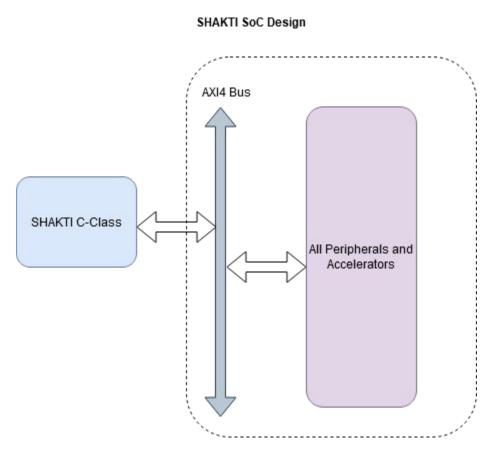

#### **SHAKTI C-Class System Level Verification**

- SHAKTI C-Class is connected to the SoC subsystem using the AXI4 interface

- SHAKTI C-Class core Verfication with Assembly test cases

- Memory Mapped Peripherals and accelerators

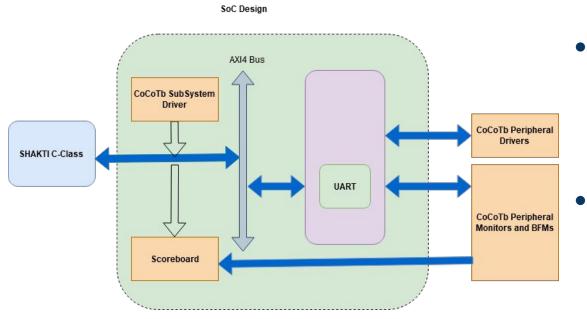

# **SHAKTI SoC Sub-System Level Verification**

- AXI4 interface as a common driver component

- By generating various AXI transactions to the sub-system, the SoC is being verified.

- The transactions can be towards verifying a Single IP or the whole interactions with the subsystem

- CoCoTb VIPs used for

Verification

#### Python based SHAKTI SoC Verification

Constraint random tests

Test bench components

Reference model development

Coverage definition

Continuous integration

# References

- RISC-V History: <u>https://riscv.org/about/history/</u>

- RISC-V Specifications <a href="https://lf-riscv.atlassian.net/wiki/spaces/HOME/pages/16154769/RISC-V+Technical+Specifications">https://lf-riscv.atlassian.net/wiki/spaces/HOME/pages/16154769/RISC-V+Technical+Specifications</a>

- Computer Organization and Design: The hardware / software interface By David A. Patterson and John L. Hennessey

- The RISC-V Reader: An Open Architecture Atlas authored by David Patterson, Andrew Waterman

- SHAKTI AAPG: https://gitlab.com/shaktiproject/tools/aapg

- riscv-dv: <u>https://github.com/google/riscv-dv</u>

- riscv-tests: <u>https://github.com/riscv/riscv-tests</u>

- riscv-torture: <u>https://github.com/ucb-bar/riscv-torture</u>

- spike: <u>https://github.com/riscv/riscv-isa-sim</u>

- CoCoTb: <u>https://www.cocotb.org/</u>

- UART CoCoTb Ext: <u>https://github.com/alexforencich/cocotbext-uart</u>

## Thank You