# GRAND CHALLENGE - 2025 IP Porting with Shakti SoC

#### DEVELOPED BY : SHAKTI DEVELOPMENT TEAM @ IITM SHAKTI.ORG.IN

### Introduction

Three variants are there to port peripheral IPs with Shakti.

#### Steps involved in porting peripheral IPs with Shakti.

- Do the following in soc.defines.

- $\circ$   $\;$  Add one more slave number for the new IP .

- Add a memory map for the same.

- Do the following in the soc.bsv or cluster file(uart\_cluster, pwm cluster, etc.) based on the implementation.

- Make one instance of the IP interface to be ported.

- Check for the memory map of the IP and set the slave number for the new IP.

- Connect AXI4(lite) of the core with peripheral's AXI4(lite).

- If necessary take the interface to the top file (fpga\_top.v).

- Take the interrupt pins to the top level or PLIC based on the implementation.

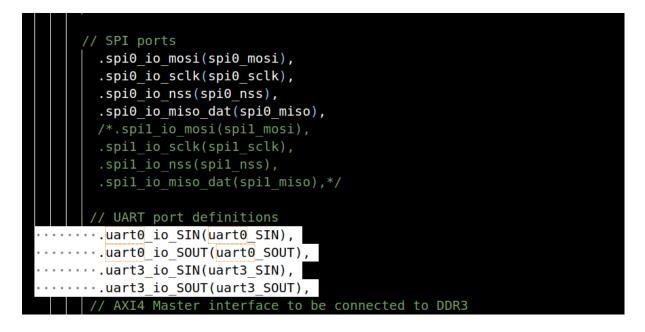

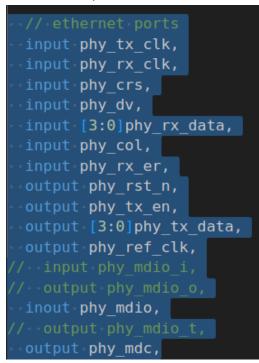

- Do the following in the fpga\_top.v

- Declare the IO pads for the peripheral.

- Map them to the mkSoc.

- If the pin(s) are bidirectional, connect them through an IO buffer.

- Do the following in the constraints.xdc.

- Add signal to pin mapping for all the IO pads.

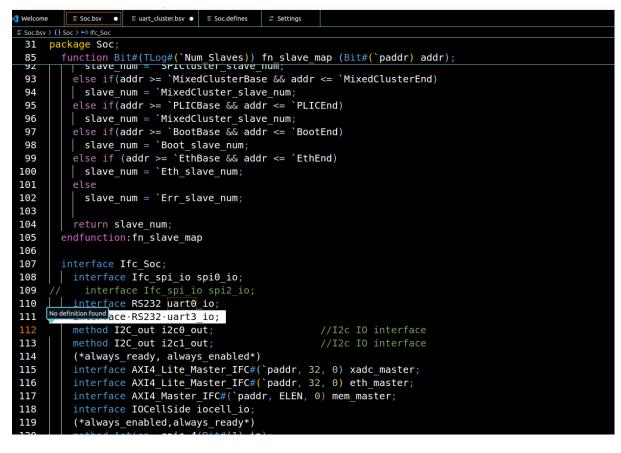

#### Integrating Slow peripherals with Shakti:

Slow peripherals operate @ lower frequencies from few Hz to few MHz (upto 25MHz). They can be integrated with Shakti core using the AXI4 Lite interface which is slow fabric.

The peripherals like SPI, UART, I2C, GPIO, etc. are interfaced with Shakti using the following logic. In addition, it is assumed that the peripheral IP is already integrated with Shakti. The objective is to add one more additional interface of the same type.

Normally these peripherals are interfaced with Core through clusters (e.g. UART Cluster, SPI cluster, PWM cluster, Mixed cluster, etc.). This section explains how to add the existing IPs to the core.

It is assumed that the shakti core is taken from sp2020 gitlab repo (https://gitlab.com/shaktiproject/sp2020).

### Hierarchy

For UART the hierarchy is as follows (leftmost is the top file),

$Soc \gets uart\_cluster$

| 🗙 Welcome   | E Soc.bsv x ≭ Settings                                                                          |

|-------------|-------------------------------------------------------------------------------------------------|

| ≣ Soc.bsv > | ( ) Soc > ( ) mkSoc                                                                             |

| 31          | package Soc; > uart_cluster Aa ab * 2of11 $\uparrow \downarrow \equiv x$                        |

| 274         | (*synthesize*)                                                                                  |

| 277         | <pre>let curr_reset&lt;-exposeCurrentReset;</pre>                                               |

| 278         | <pre>Ifc_ccore_axi4 ccore &lt;- mkccore_axi4(`resetpc, 0);</pre>                                |

| 279         |                                                                                                 |

| 280         | AXI4_Fabric_IFC #(`Num_Fast_Masters, `Num_Fast_Slaves, `paddr, ELEN, USERSPACE)                 |

| 281         | <pre>fabric &lt;- mkAXI4_Fabric     (fn_slave_map_fast);</pre>                                  |

| 282         | <pre>Ifc_clint_axi4#(`paddr, ELEN, 0, 1, 256) clint &lt;- mkclint_axi4();</pre>                 |

| 283         | <pre>Ifc_debug_halt_loop_axi4#(`paddr, ELEN, USERSPACE) debug_memory &lt;-</pre>                |

|             | mkdebug_halt_loop_axi4;                                                                         |

| 284         | <pre>Ifc_err_slave_axi4#(`paddr,ELEN,0) fast_err_slave &lt;- mkerr_slave_axi4;</pre>            |

| 285         |                                                                                                 |

| 286         | AXI4_Lite_Fabric_IFC #(`Num_Masters, `Num_Slaves, `paddr, 32, USERSPACE)                        |

| 287         | slow_fabric <- mkAXI4_Lite_Fabric // (fn_slave_map);                                            |

| 288         | Ifc_pwm_cluster pwm_cluster <- mkpwm_cluster;                                                   |

| 289         | <pre>Ifc_uart_cluster uart_cluster <mkuart_cluster;< pre=""></mkuart_cluster;<></pre>           |

| 290         | <pre>Ifc_spi_cluster spi_cluster &lt;- mkspi_cluster;</pre>                                     |

| 291         | <pre>Ifc_mixed_cluster mixed_cluster &lt;- mkmixed_cluster;</pre>                               |

| 292         | <pre>Ifc_err_slave_axi4lite#(`paddr,32,0) err_slave &lt;- mkerr_slave_axi4lite;</pre>           |

| 293         | <pre>Ifc_bram_axi4lite#(`paddr, 32, 0, 13) boot &lt;- mkbram_axi4lite('h1000, "boot.mem",</pre> |

|             | "Boot");                                                                                        |

| 294         | <pre>Wire#(Bit#(3)) wr_ext_interrupts &lt;- mkWire();</pre>                                     |

| 295         |                                                                                                 |

| 296         | <pre>Wire#(Bit#(1)) wr_gpio4_in &lt;- mkDWire(0);</pre>                                         |

| 297         | <pre>Wire#(Bit#(1)) wr_gpio7_in &lt;- mkDWire(0);</pre>                                         |

| 298         | <pre>Wire#(Bit#(1)) wr_gpio8_in &lt;- mkDWire(0);</pre>                                         |

| 299         | <pre>Wire#(Bit#(1)) wr_gpio14_in &lt;- mkDWire(0);</pre>                                        |

| 300         | <pre>Wire#(Bit#(1)) wr_gpio15_in &lt;- mkDWire(0);</pre>                                        |

| 201         |                                                                                                 |

All the Memory mapping details will be in the Soc.defines file.

| 🗙 Welcome | ≣ Soc.b | osv   | ≣ Soc.defines × |           |      |  |  |              |    |      |          |      |     |  |

|-----------|---------|-------|-----------------|-----------|------|--|--|--------------|----|------|----------|------|-----|--|

|           |         |       |                 |           |      |  |  |              |    |      |          |      |     |  |

|           |         |       | rr_slave_n      |           |      |  |  | uart_cluster | Aa | ab * | No resul | ts 1 | ≓ × |  |

|           | efine   | Slow_ | _fabric_sla     | ve_num 4  |      |  |  |              |    |      |          |      |     |  |

| 12        |         |       |                 |           |      |  |  |              |    |      |          |      |     |  |

|           | efine   |       | •               | 'h8000_   |      |  |  |              |    |      |          |      |     |  |

|           | efine   |       | 2               | 'h8FFF_   | FFFF |  |  |              |    |      |          |      |     |  |

| 15 `d     | efine   | Clint | Base            | 'h0200_   | 9000 |  |  |              |    |      |          |      |     |  |

| 16 `d     | efine   | Clint | End             | 'h020B_   | FFFF |  |  |              |    |      |          |      |     |  |

| 17 `d     | efine   | Debug | Base            | 'h0000_   | 9010 |  |  |              |    |      |          |      |     |  |

| 18 `d     | efine   | Debug | JEnd            | 'h0000_   | 901F |  |  |              |    |      |          |      |     |  |

| 19 `d     | efine   | SlowE | lase            | 'h0000_   | 1000 |  |  |              |    |      |          |      |     |  |

| 20 `d     | efine   | SlowE | nd              | 'h0004_   | 7FFF |  |  |              |    |      |          |      |     |  |

| 21        |         |       |                 |           |      |  |  |              |    |      |          |      |     |  |

| 22 `d     | efine   | Num_M | lasters 1       |           |      |  |  |              |    |      |          |      |     |  |

| 23        |         |       |                 |           |      |  |  |              |    |      |          |      |     |  |

| 24 `d     | efine   | Num S | Slaves 7        |           |      |  |  |              |    |      |          |      |     |  |

| 25 `d     | efine   | PWMCl | uster slav      | e num 0   |      |  |  |              |    |      |          |      |     |  |

| 26 `d     | efine   | UARTO | luster sla      | ve num 1  |      |  |  |              |    |      |          |      |     |  |

| 27 `d     | efine   | SPICl | uster slav      | e num 2   |      |  |  |              |    |      |          |      |     |  |

| 28 `d     | efine   | Mixed | Cluster sl      | ave num 3 |      |  |  |              |    |      |          |      |     |  |

| 29 `d     | efine   | Boot  | slave num       | 4         |      |  |  |              |    |      |          |      |     |  |

| 30 `d     | efine   | Eth s | lave num 5      |           |      |  |  |              |    |      |          |      |     |  |

| 31 `d     | efine   | Errs  | lave num 6      |           |      |  |  |              |    |      |          |      |     |  |

| 32        |         |       |                 |           |      |  |  |              |    |      |          |      |     |  |

| 33 `d     | efine   | BootE | lase            | 'h0000    | 1000 |  |  |              |    |      |          |      |     |  |

| 34 `d     | efine   | BootE | nd              | 'h0000    |      |  |  |              |    |      |          |      |     |  |

| 35 `d     | efine∙  | UARTO | lusterBase      | _         |      |  |  |              |    |      |          |      |     |  |

|           |         |       | lusterEnd       |           |      |  |  |              |    |      |          |      |     |  |

|           |         |       | usterBase       | 'h0002    |      |  |  |              |    |      |          |      |     |  |

|           |         |       | usterEnd        | 'h0002_   |      |  |  |              |    |      |          |      |     |  |

|           |         |       | usterBase       | 'h0003    |      |  |  |              |    |      |          |      |     |  |

| 40 `d     |         |       | uctorEnd        | 160003_   |      |  |  |              |    |      |          |      |     |  |

### Memory Mapping

All the slow peripherals will be placed in the range of Slow fabric memory allocation. UART peripheral also will fall in this range.

| 🗙 Welcom | ne ≣ Soc.bsv ≣ Soc.defines × ₹                              | E Settings  |                |                   | •••               |

|----------|-------------------------------------------------------------|-------------|----------------|-------------------|-------------------|

| ≡ Soc.de | fines                                                       |             |                |                   |                   |

| 5        |                                                             |             | > uart_cluster | Aa_ab* No results | $\wedge = \times$ |

| 6        | <pre>`define Num_Fast_Slaves 5</pre>                        |             |                |                   |                   |

| 7        | <pre>`define Memory_slave_num</pre>                         |             |                |                   |                   |

| 8        | `define Clint_slave_num 1                                   |             |                |                   |                   |

| 9        | <pre>`define Debug_slave_num 2 `define FeetFeetended"</pre> |             |                |                   |                   |

| 10       | <pre>`define FastErr_slave_num</pre>                        |             |                |                   | -                 |

| 11       | `define Slow_fabric_slave                                   | _num 4      |                |                   |                   |

| 12       |                                                             |             |                |                   |                   |

| 13       | <pre>`define MemoryBase</pre>                               | 'h8000_0000 |                |                   |                   |

| 14       | <pre>`define MemoryEnd `define ClietDees</pre>              | 'h8FFF_FFFF |                |                   |                   |

| 15       | <pre>`define ClintBase</pre>                                | 'h0200_0000 |                |                   |                   |

| 16       | `define ClintEnd                                            | 'h020B_FFFF |                |                   |                   |

| 17       | `define DebugBase                                           | 'h0000_0010 |                |                   |                   |

| 18       | `define DebugEnd                                            | 'h0000_001F |                |                   |                   |

| 19       | <pre>`define SlowBase</pre>                                 | 'h0000_1000 |                |                   |                   |

| 20       | `define SlowEnd                                             | 'h0004_7FFF |                |                   |                   |

| 21       |                                                             |             |                |                   |                   |

| 22       | `define Num_Masters 1                                       |             |                |                   |                   |

| 23       | define Num Clause 7                                         |             |                |                   |                   |

| 24       | <pre>`define Num_Slaves 7 `define NumCluster slave</pre>    |             |                |                   |                   |

| 25       | <pre>`define PWMCluster_slave_</pre>                        |             |                |                   |                   |

| 26       | `define.UARTCluster_slave                                   | _           |                |                   |                   |

| 27       | <pre>`define SPICluster_slave_</pre>                        |             |                |                   |                   |

| 28       | <pre>`define MixedCluster_slav</pre>                        | e_num 3     |                |                   |                   |

| 29       | <pre>`define Boot_slave_num 4 `define Fth_clave_num F</pre> |             |                |                   |                   |

| 30       | <pre>`define Eth_slave_num 5 `define Err clave num 6</pre>  |             |                |                   |                   |

| 31       | `define Err_slave_num 6                                     |             |                |                   |                   |

| 32       | define ReetRace                                             | 1000 1000   |                |                   |                   |

| 33       | <pre>`define BootBase `define BootEnd</pre>                 | 'h0000_1000 |                |                   |                   |

| 34       | <pre>`define BootEnd `define UAPTClusterBase</pre>          | 'h0000_2FFF |                |                   |                   |

|          |                                                             |             |                |                   |                   |

In this file the Slow fabric memory allocation has further separate memory range allocated for UART instances alone which is termed as UART cluster, all the memory mapping of the UART instances will be in this range.

Slow fabric  $\rightarrow$  UART cluster  $\rightarrow$  UART instance

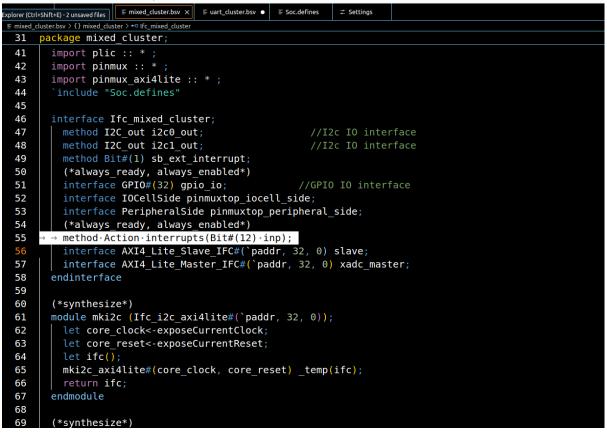

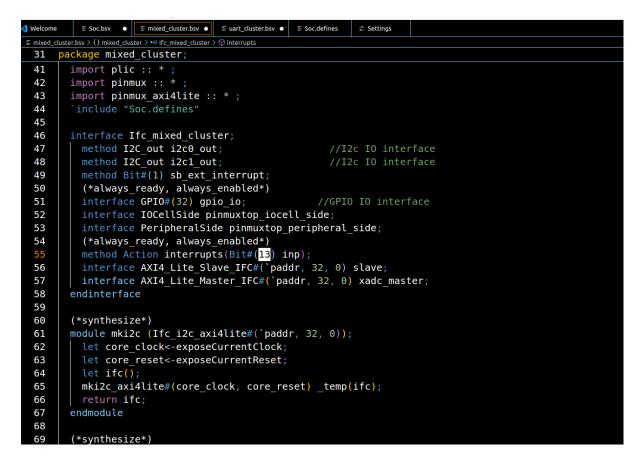

Same like UART clusters there are also clusters for SPI and PWM to accommodate SPI & PWM IPs, all the remaining peripherals will be placed in the Mixed cluster.

### Adding one more cluster IP:

This section shows the integration for one more UART IP in the UART cluster. The files that needs to be modified are

- soc.bsv

- soc.defines

- uart\_cluster.bsv

- mixed\_cluster.bsv

- fpga\_top.v

• constraints.xdc

### 1. Make the following changes in the "soc.defines".

#### Step 1 (Increase the UART Cluster memory range):

Increase the UART Cluster memory map from

| 🗙 Welcom  | e ≣ Soc.bsv 🛛 🗄 Soc.defines ● 🚅      | Settings      |   |                |                      | ш                     |

|-----------|--------------------------------------|---------------|---|----------------|----------------------|-----------------------|

| ≡ Soc.def | ines                                 | -             |   |                |                      |                       |

| 33        | `define BootBase                     | 'h0000_1000   |   | > uart_cluster | Aa ab * No results 1 | $\downarrow = \times$ |

| 34        | `define BootEnd                      | 'h0000_2FFF   | l |                |                      |                       |

| 35        | `define.UARTClusterBase              | •'h0001_1300  |   |                |                      |                       |

| 36        | `define UARTClusterEnd · · ·         | • 'h0001_1540 |   |                |                      |                       |

| 37        | `define SPIClusterBase               | 'h0002_0000   |   |                |                      |                       |

| 38        | `define SPIClusterEnd                | 'h0002_01FF   |   |                |                      |                       |

| 39        | `define PWMClusterBase               | 'h0003_0000   |   |                |                      |                       |

| 40        | <pre>`define PWMClusterEnd</pre>     | 'h0003_05FF   |   |                |                      | _                     |

| 41        | `define MixedClusterBase             | 'h0004_0000   |   |                |                      |                       |

| 42        | <pre>`define MixedClusterEnd</pre>   | 'h0004_15FF   |   |                |                      |                       |

| 43        | `define EthBase                      | 'h0004_4000   |   |                |                      |                       |

| 44        | `define EthEnd                       | 'h0004_7FFF   |   |                |                      |                       |

| 45        |                                      |               |   |                |                      |                       |

| 46        | // - PWM cluster                     |               |   |                |                      |                       |

| 47        | `define PWMCluster_Num_Sl            | aves 7        |   |                |                      |                       |

| 48        | <pre>`define PWMCluster_Num_Ma</pre> | sters 1       |   |                |                      |                       |

| 49        |                                      |               |   |                |                      |                       |

| 50        | <pre>`define PWM0_slave_num 0</pre>  |               |   |                |                      |                       |

| 51        | <pre>`define PWM1_slave_num 1</pre>  |               |   |                |                      |                       |

| 52        | <pre>`define PWM2_slave_num 2</pre>  |               |   |                |                      |                       |

| 53        | <pre>`define PWM3_slave_num 3</pre>  |               |   |                |                      |                       |

| 54        | `define PWM4_slave_num 4             |               |   |                |                      |                       |

| 55        | <pre>`define PWM5_slave_num 5</pre>  |               |   |                |                      |                       |

| 56        |                                      |               |   |                |                      |                       |

| 57        | `define PWMCluster_err_sl            | ave_num 6     |   |                |                      |                       |

| 58        |                                      |               |   |                |                      |                       |

| 59        | `define PWM0Base 'h00                | 03_0000       |   |                |                      |                       |

| 60        | `define PWM0End 'h00                 | 03_00FF       |   |                |                      |                       |

| 61        | `define PWM1Base 'h00                | 03_0100       |   |                |                      |                       |

| 62        | `define PWM1End 'h00                 | 03_01FF       |   |                |                      |                       |

|           |                                      |               |   |                |                      |                       |

| 🗙 Welcom | ne ≣ Soc.bsv ≣ Soc.defines ● 🗟 | 2 Settings   |                | □ …                                                   |

|----------|--------------------------------|--------------|----------------|-------------------------------------------------------|

| ≡ Soc.de |                                |              |                |                                                       |

| 31       | `define Err_slave_num 6        |              | > uart_cluster | Aa ab $*$ No results $\land \downarrow \equiv \times$ |

| 32       |                                |              |                |                                                       |

| 33       | `define BootBase               | 'h0000_1000  |                |                                                       |

| 34       | `define BootEnd                | 'h0000_2FFF  |                |                                                       |

| 35       | `define UARTClusterBase        | 'h0001_1300_ |                |                                                       |

| 36       | `define.UARTClusterEnd         | ·'h0001_1640 |                |                                                       |

| 37       | `define SPIClusterBase         | 'h0002_0000  |                |                                                       |

| 38       | `define SPIClusterEnd          | 'h0002_01FF  |                |                                                       |

| 39       | `define PWMClusterBase         | 'h0003_0000  |                |                                                       |

| 40       | `define PWMClusterEnd          | 'h0003_05FF  |                |                                                       |

| 41       | `define MixedClusterBase       | 'h0004_0000  |                |                                                       |

| 42       | `define MixedClusterEnd        | 'h0004_15FF  |                |                                                       |

| 43       | `define EthBase                | 'h0004_4000  |                |                                                       |

| 44       | `define EthEnd                 | 'h0004_7FFF  |                |                                                       |

| 45       |                                |              |                |                                                       |

| 46       | // - PWM cluster               |              |                |                                                       |

| 47       | `define PWMCluster_Num_Sl      | aves 7       |                |                                                       |

| 48       | `define PWMCluster_Num_Ma      | sters 1      |                |                                                       |

| 49       |                                |              |                |                                                       |

| 50       | `define PWM0_slave_num 0       |              |                |                                                       |

| 51       | `define PWM1_slave_num 1       |              |                |                                                       |

| 52       | `define PWM2_slave_num 2       |              |                |                                                       |

| 53       | `define PWM3_slave_num 3       |              |                |                                                       |

| 54       | `define PWM4 slave num 4       |              |                |                                                       |

| 55       | `define PWM5 slave num 5       |              |                |                                                       |

| 56       |                                |              |                |                                                       |

| 57       | `define PWMCluster_err_sl      | ave_num 6    |                |                                                       |

| 58       |                                |              |                |                                                       |

| 59       | `define PWM0Base 'h00          | 03 0000      |                |                                                       |

| 60       | `define PWM0End 'h00           | 03_00FF      |                |                                                       |

|          |                                |              |                |                                                       |

Step 2 (Increase the number of UART slaves): Increase the "UARTCluster\_Num\_Slaves" from 4 to 5.

| Welcome                                                                          | □ … |

|----------------------------------------------------------------------------------|-----|

| ≣ Soc.defines                                                                    |     |

| 80 $\downarrow$ wart_cluster Aa $\Rightarrow$ No results $\uparrow \downarrow =$ | ×   |

|                                                                                  |     |

|                                                                                  |     |

| 82 `define SPI0End 'h0002_00FF                                                   |     |

| 83 `define SPI1Base 'h0002_0100                                                  |     |

| 84 `define SPI1End 'h0002_01FF                                                   |     |

| 85 //`define SPI2Base 'h0002_0200                                                |     |

| 86 //`define SPI2End 'h0002_02FF                                                 |     |

|                                                                                  |     |

| 88 // - UART cluster                                                             |     |

| 89 `define UARTCluster_Num_Slaves 4                                              |     |

| 90 `define UARTCluster_Num_Masters 1                                             |     |

|                                                                                  |     |

| 92 `define UARTO_slave_num 0                                                     |     |

| 93 `define UART1_slave_num 1                                                     |     |

| 94 `define UART2_slave_num 2                                                     |     |

| 95 `define UARTCluster_err_slave_num 3                                           |     |

|                                                                                  |     |

| 97 `define UART0Base 'h0001_1300                                                 |     |

| 98 `define UART0End 'h0001_1340                                                  |     |

| 99 `define UART1Base 'h0001_1400                                                 |     |

| 100 `define UART1End 'h0001_1440                                                 |     |

| 101 `define UART2Base 'h0001_1500                                                |     |

| 102 `define UART2End 'h0001_1540                                                 |     |

| 103                                                                              |     |

| 104 // - Mixed Cluster                                                           |     |

| 105 `define MixedCluster_Num_Slaves 7                                            |     |

| 106 `define MixedCluster_Num_Masters 1                                           |     |

| 107                                                                              |     |

| 108 `define I2C0_slave_num 0                                                     |     |

| 109 `define T2C1 slave num 1                                                     |     |

From "4" to "5".

| 🗙 Welcom | ne E Soc.bsv E Soc.defines ● Z Settings                              | □ …                                                         |

|----------|----------------------------------------------------------------------|-------------------------------------------------------------|

| ≡ Soc.de |                                                                      |                                                             |

| /9       | derine Spicluster_err_stave_num 2                                    | > uart_cluster Aa ab * No results $\uparrow \downarrow = x$ |

| 80       |                                                                      |                                                             |

| 81       | <pre>`define SPI0Base 'h0002_0000 `define SPI0Fad</pre>              |                                                             |

| 82       | <pre>`define SPI0End 'h0002_00FF `define SPI0End 'h0002_0100</pre>   |                                                             |

| 83       | <pre>`define SPI1Base 'h0002_0100 `define SPI1Ead</pre>              |                                                             |

| 84       | <pre>`define SPI1End 'h0002_01FF (/`define SPI2Base h0002_0200</pre> |                                                             |

| 85       | <pre>//`define SPI2Base 'h0002_0200 //`define SPI2Ead</pre>          |                                                             |

| 86       | //`define SPI2End 'h0002_02FF                                        |                                                             |

| 87       |                                                                      |                                                             |

| 88       | // - UART cluster                                                    |                                                             |

| 89       | <pre>`define UARTCluster_Num_Slaves 5</pre>                          |                                                             |

| 90       | `define UARTCluster_Num_Masters 1                                    |                                                             |

| 91<br>92 | define HADTO slave num O                                             |                                                             |

| 92       | `define UART0_slave_num 0<br>`define UART1 slave num 1               |                                                             |

| 93<br>94 | define UART2 slave num 2                                             |                                                             |

| 94<br>95 |                                                                      |                                                             |

| 95<br>96 | `define UARTCluster_err_slave_num 3                                  |                                                             |

| 90<br>97 | `define UART0Base 'h0001_1300                                        |                                                             |

| 98       | define UARTOEnd 'h0001 1340                                          |                                                             |

| 99       | define UARTIBase 'h0001 1400                                         |                                                             |

| 100      | define UARTIEnd 'h0001 1440                                          |                                                             |

| 101      | define UART2Base 'h0001 1500                                         |                                                             |

| 101      | define UART2End 'h0001 1540                                          |                                                             |

| 102      |                                                                      |                                                             |

| 104      | // - Mixed Cluster                                                   |                                                             |

| 105      | define MixedCluster Num Slaves 7                                     |                                                             |

| 106      | `define MixedCluster_Num_Masters 1                                   |                                                             |

| 100      |                                                                      |                                                             |

| 108      | `define I2C0 slave num 0                                             |                                                             |

| 100      | <pre>`define I2C1 slave num 1</pre>                                  |                                                             |

|          |                                                                      |                                                             |

#### Step 3 (Add slave number for the new UART IP):

Add a slave number for the new slave UART. i.e. Change the

| X Welcome                                                                     | □ …             |

|-------------------------------------------------------------------------------|-----------------|

| E Soc.defines                                                                 |                 |

| /9 define Spiciuster_err_stave_num 2<br>> uart_duster Aa ab .* No results ↑ ↓ | $\equiv \times$ |

|                                                                               |                 |

| 81 `define SPI0Base 'h0002_0000                                               |                 |

| 82 `define SPI0End 'h0002_00FF                                                |                 |

| 83 `define SPI1Base 'h0002_0100                                               |                 |

| 84 `define SPI1End 'h0002_01FF                                                |                 |

| 85 //`define SPI2Base 'h0002_0200                                             |                 |

| 86 //`define SPI2End 'h0002_02FF                                              |                 |

| 87                                                                            |                 |

| 88 // - UART cluster                                                          |                 |

| 89 `define UARTCluster_Num_Slaves 4                                           |                 |

| 90 `define UARTCluster_Num_Masters 1                                          |                 |

| 91                                                                            |                 |

| 92 `define.UARTO_slave_num.0                                                  |                 |

| 93 `define.UART1_slave_num.1                                                  |                 |

| 94 `define UART2_slave_num 2                                                  |                 |

| 95 `define.UARTCluster_err_slave_num.3                                        |                 |

| 96                                                                            |                 |

| 97 `define UART0Base 'h0001_1300                                              |                 |

| 98 `define UART0End 'h0001_1340                                               |                 |

| 99 `define UART1Base 'h0001_1400                                              |                 |

| 100 `define UART1End 'h0001_1440                                              |                 |

| 101 `define UART2Base 'h0001_1500                                             |                 |

| 102 `define UART2End 'h0001_1540                                              |                 |

| 103                                                                           |                 |

| 104 // - Mixed Cluster                                                        |                 |

| 105 `define MixedCluster_Num_Slaves 7                                         |                 |

| 106 `define MixedCluster_Num_Masters 1                                        |                 |

| 107                                                                           |                 |

| 108 `define I2C0_slave_num 0                                                  |                 |

| 109 `define T2C1 slave num 1                                                  |                 |

| 🗙 Welcon | ne E Soc.bsv E uart_cluster.bsv ● E Soc.defines X Z Settings |                        | □ …                              |

|----------|--------------------------------------------------------------|------------------------|----------------------------------|

| ≣ Soc.de | fines                                                        |                        |                                  |

| 81       | `define SPI0Base                                             | > uart0 Aa ab * 1 of 3 | $\uparrow  \downarrow =  \times$ |

| 82       | `define SPI0End 'h0002_00FF                                  |                        |                                  |

| 83       | `define SPI1Base 'h0002_0100                                 |                        |                                  |

| 84       | `define SPI1End                                              |                        |                                  |

| 85       | <pre>//`define SPI2Base 'h0002_0200</pre>                    |                        |                                  |

| 86       | //`define SPI2End 'h0002_02FF                                |                        |                                  |

| 87       |                                                              |                        |                                  |

| 88       | // - UART cluster                                            |                        |                                  |

| 89       | <pre>`define UARTCluster_Num_Slaves 5</pre>                  |                        |                                  |

| 90       | <pre>`define UARTCluster_Num_Masters 1</pre>                 |                        |                                  |

| 91       |                                                              |                        |                                  |

| 92       | `define UART0_slave_num 0                                    |                        |                                  |

| 93       | <pre>`define UART1_slave_num 1</pre>                         |                        |                                  |

| 94       | `define UART2_slave_num 2                                    |                        |                                  |

| 95       | `define UART3_slave_num 3                                    |                        |                                  |

| 96       | <pre>`define UARTCluster_err_slave_num 4</pre>               |                        |                                  |

| 97       |                                                              |                        |                                  |

| 98       | `define UART0Base                                            |                        |                                  |

| 99       | `define UART0End                                             |                        |                                  |

| 100      | `define UART1Base 'h0001_1400                                |                        |                                  |

| 101      | `define UART1End                                             |                        |                                  |

| 102      | `define UART2Base                                            |                        |                                  |

| 103      | `define UART2End                                             |                        |                                  |

| 104      | `define UART3Base 'h0001_1600                                |                        |                                  |

| 105      | `define UART3End                                             |                        |                                  |

| 106      |                                                              |                        |                                  |

| 107      | // - Mixed Cluster                                           |                        |                                  |

| 108      | <pre>`define MixedCluster_Num_Slaves 7</pre>                 |                        |                                  |

| 109      | `define MixedCluster_Num_Masters 1                           |                        |                                  |

| 110      |                                                              |                        |                                  |

|          |                                                              |                        |                                  |

**Step 4 (Add memory range for the new UART being added):** Add a memory map to the new UART.

| 🗙 Welcome   | ≣ Soc.bsv     | ≡ Soc.defines ●    |                        |   |                |                    |       | □ … |

|-------------|---------------|--------------------|------------------------|---|----------------|--------------------|-------|-----|

| ≡ Soc.defin | es            |                    |                        |   |                |                    |       |     |

| 79<br>80    | derine SPic   | luster_err_        | stave_num              | 2 | > uart_cluster | Aa _ab* No results | ↑ ↓ ≡ | ×   |

|             | define SPI0   | Bace 'b            | 0002 0000              |   |                |                    |       |     |

|             | define SPI0   |                    | 0002_0000<br>0002_00FF |   |                |                    |       |     |

|             | define SPI1   |                    | 0002_0001              |   |                |                    |       |     |

|             | define SPI1   |                    | 0002_0100<br>0002 01FF |   |                |                    |       |     |

|             | //`define SP: |                    | 'h0002 020             | Θ |                |                    |       |     |

| -           | //`define SP: |                    | 'h0002_02F             |   |                |                    |       |     |

| 87          | y actine bi.  |                    | 110002_021             | • |                |                    |       |     |

|             | // - UART clu | uster              |                        |   |                |                    |       |     |

| -           | define UART   |                    | Slaves 5               |   |                |                    |       |     |

| 90          | define UART   |                    |                        |   |                |                    |       |     |

| 91          |               |                    |                        |   |                |                    |       |     |

|             | define UART   | 0 slave num        | Θ                      |   |                |                    |       |     |

|             | define UART   |                    |                        |   |                |                    |       |     |

|             | define UART   |                    |                        |   |                |                    |       |     |

|             | define UART   |                    |                        |   |                |                    |       |     |

|             | define UART   |                    |                        | 4 |                |                    |       |     |

| 97          |               |                    |                        |   |                |                    |       |     |

| 98          | define UART   | 9Base∙∙∙∙'         | h0001_1300             |   |                |                    |       |     |

| 99          | define UART   | 9End · · · · · · ' | h0001_1340             |   |                |                    |       |     |

| 100         | define UART   | 1Base·····         | h0001_1400             |   |                |                    |       | -   |

| 101         | define UART   | 1End · · · · · · ' | h0001_1440             |   |                |                    |       |     |

| 102         | define UART2  | 2Base·····         | h0001_1500             |   |                |                    |       |     |

| 103         | define UART2  | 2End · · · · · · ' | h0001_1540             |   |                |                    |       |     |

| 104         |               |                    |                        |   |                |                    |       |     |

| 105 ,       | // - Mixed C  | luster             |                        |   |                |                    |       |     |

| 106         | define Mixed  | dCluster_Nu        | m_Slaves 7             |   |                |                    |       |     |

|             | define Mixed  | dCluster_Nu        | m_Masters              | 1 |                |                    |       |     |

| 108         |               |                    |                        |   |                |                    |       |     |

| 109         | define T2C0   | slave num          | 0                      |   |                |                    |       |     |

i.e . Add memory map

| 🗙 Welcom   | e ≣ Soc.bsv                          | E Soc.defines ● |             |   |                |                      | Π                       |

|------------|--------------------------------------|-----------------|-------------|---|----------------|----------------------|-------------------------|

| ≡ Soc.de   |                                      | _ bockdennes •  | a seconds   |   |                |                      |                         |

| /9         | derine SPic                          | tuster_err_     | scave_num   | 2 | > uart_cluster | Aa _ab_ * No results | $\wedge \downarrow = x$ |

| 80         |                                      |                 |             |   | , <u></u>      | Horesaus             | - + + - ×               |

| 81         | `define SPI0                         |                 | 10002_0000  |   |                |                      |                         |

| 82         | `define SPI0                         |                 | 10002_00FF  |   |                |                      |                         |

| 83         | `define SPI1                         |                 | 10002_0100  |   |                |                      |                         |

| 84         | `define SPI1                         |                 | 10002_01FF  |   |                |                      |                         |

| 85         | <pre>//`define SP</pre>              |                 | 'h0002_020  |   |                |                      |                         |

| 86         | <pre>//`define SP</pre>              | I2End           | 'h0002_02F  | F |                |                      |                         |

| 87         | -                                    |                 |             |   |                |                      |                         |

| 88         | // - UART cl                         |                 | -           |   |                |                      |                         |

| 89         | `define UART                         |                 |             |   |                |                      |                         |

| 90         | `define UART                         | Cluster_Num     | n_Masters 1 |   |                |                      |                         |

| 91         |                                      |                 | -           |   |                |                      |                         |

| 92         | `define UART                         |                 |             |   |                |                      |                         |

| 93         | `define UART                         |                 |             |   |                |                      |                         |

| 94         | `define UART                         | _               |             |   |                |                      |                         |

| 95         | `define UART                         |                 |             |   |                |                      |                         |

| 96         | `define UART                         | Cluster_err     | _slave_num  | 4 |                |                      |                         |

| 97         |                                      |                 |             |   |                |                      |                         |

| 98         | \define UART                         |                 | h0001_1300  |   |                |                      |                         |

| 99         | `define UART                         |                 | h0001_1340  |   |                |                      |                         |

| 100        | `define UART                         |                 | h0001_1400  |   |                |                      |                         |

| 101        | `define UART                         |                 | h0001_1440  |   |                |                      |                         |

| 102        | `define UART                         |                 | h0001_1500  |   |                |                      |                         |

| 103        | `define UART<br>`define∙UART         |                 | h0001_1540  |   |                |                      |                         |

| 104        |                                      |                 | _           |   |                |                      |                         |

| 105        | `define UART                         | SEIIU · · · · · | 10001_1040  |   |                |                      |                         |

| 106<br>107 | // Mixed C                           | luctor          |             |   |                |                      |                         |

| 107        | <pre>// - Mixed C `define Mixe</pre> |                 |             |   |                |                      |                         |

|            | `define Mixe                         |                 |             |   |                |                      |                         |

|            |                                      |                 |             |   |                |                      |                         |

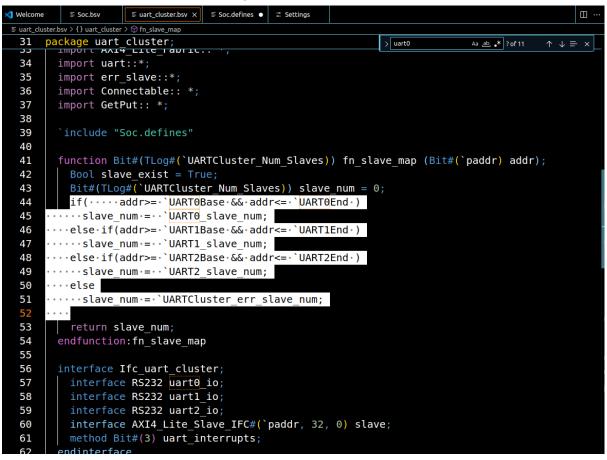

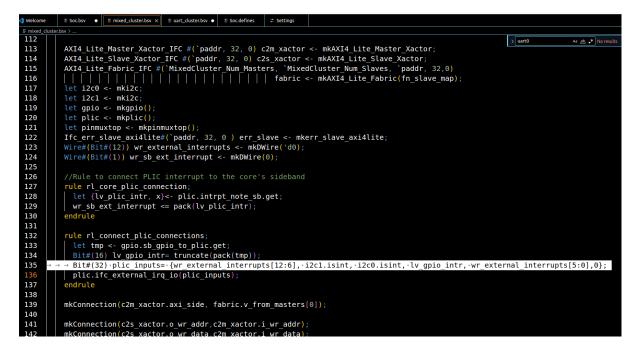

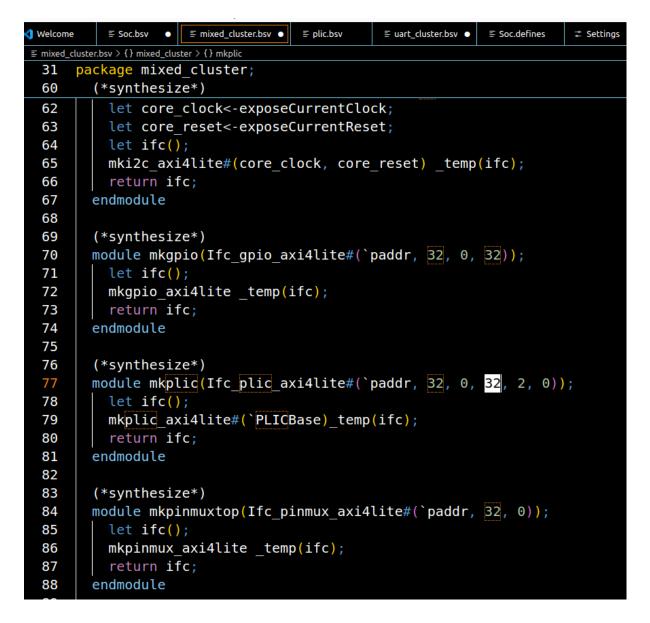

### 2. Make the following changes in the "uart\_cluster.bsv"

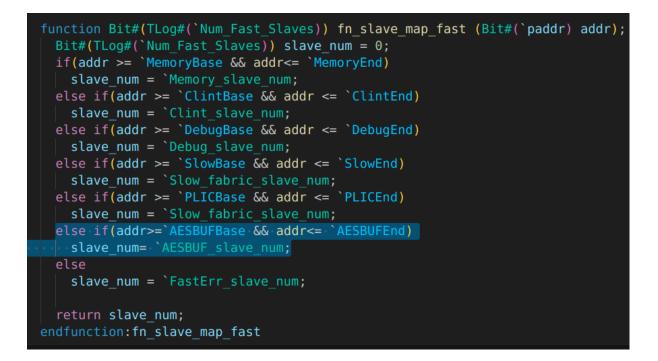

#### Step 1 (Add condition for memory range check ):

Add if condition for new uart i.e. change the code from

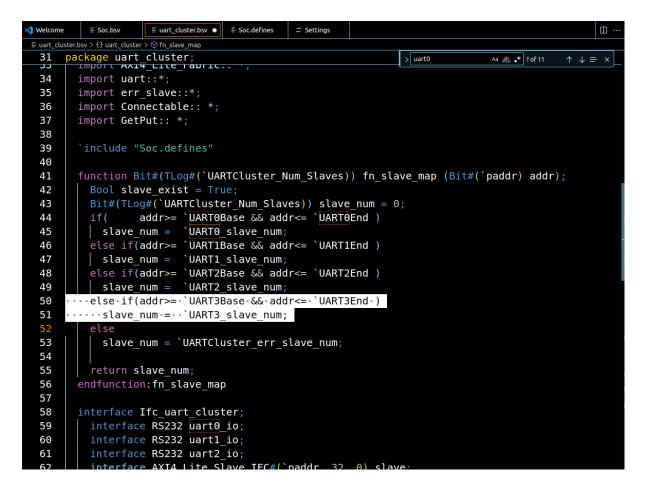

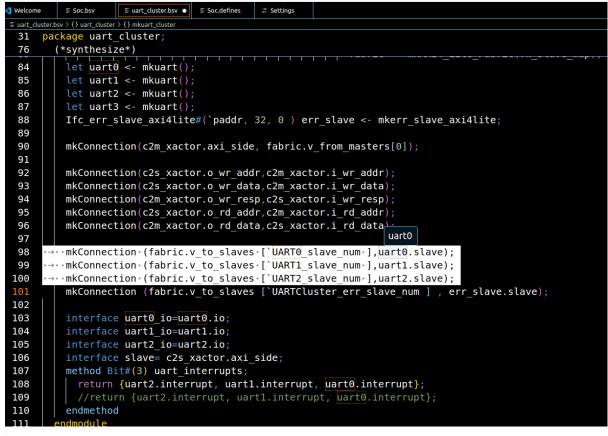

**Step 2 (Make one more instance for new UART):** Add UART Interface i.e. Change the code from

| 🗙 Welcome  | E Soc.bsv E uart_cluster.bsv ● E Soc.defines Z Settings                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|

| ≡ uart_clu | ster.bsv > () uart_cluster > +0 lfc_uart_cluster                                                                                    |

| 31         | package uart_cluster; $\Rightarrow$ varto $A_{a} \stackrel{\text{de}}{\longrightarrow} *$ of 11 $\uparrow \downarrow \equiv \times$ |

| 41         | <pre>function Bit#(TLog#(`UARTCluster_Num_Slaves)) fn_slave_map (Bit#(`paddr) addr);</pre>                                          |

| 55         | return slave num;                                                                                                                   |

| 56         | endfunction:fn_slave map                                                                                                            |

| 57         |                                                                                                                                     |

| 58         | interface Ifc uart cluster;                                                                                                         |

| 59         | ••••interface RS232 uart0 io;                                                                                                       |

| 60         | ••••interface•RS232•uart1 io;                                                                                                       |

| 61         | ••••interface•RS232•uart2_io;                                                                                                       |

| 62         | <pre>interface AXI4_Lite_Slave_IFC#(`paddr, 32, 0) slave;</pre>                                                                     |

| 63         | <pre>method Bit#(3) uart_interrupts;</pre>                                                                                          |

| 64         | endinterface                                                                                                                        |

| 65         |                                                                                                                                     |

| 66         | (*synthesize*)                                                                                                                      |

| 67         | <pre>module mkuart(Ifc_uart_axi4lite#(32, 32, 0, 16));</pre>                                                                        |

| 68         | <pre>let core_clock&lt;-exposeCurrentClock;</pre>                                                                                   |

| 69         | <pre>let core_reset&lt;-exposeCurrentReset;</pre>                                                                                   |

| 70         | let ifc();                                                                                                                          |

| 71         | <pre>mkuart_axi4lite#(core_clock, core_reset, 163, 0, 0) _temp(ifc);</pre>                                                          |

| 72         | return ifc;                                                                                                                         |

| 73         | endmodule                                                                                                                           |

| 74         |                                                                                                                                     |

| 75         | (*synthesize*)                                                                                                                      |

| 76         | <pre>module mkuart_cluster(Ifc_uart_cluster);</pre>                                                                                 |

| 77         | <pre>let curr_clk&lt;- exposeCurrentClock;</pre>                                                                                    |

| 78         | <pre>let curr_reset &lt;- exposeCurrentReset;</pre>                                                                                 |

| 79         | AXI4_Lite_Master_Xactor_IFC #(`paddr, 32, 0) c2m_xactor <- mkAXI4_Lite_Master_Xactor;                                               |

| 80         | AXI4_Lite_Slave_Xactor_IFC #(`paddr, 32, 0) c2s_xactor <- mkAXI4_Lite_Slave_Xactor;                                                 |

| 81         | AXI4_Lite_Fabric_IFC #(`UARTCluster_Num_Masters, `UARTCluster_Num_Slaves, `paddr, 32,                                               |

|            | 0)                                                                                                                                  |

| 🗙 Welcome | E Soc.bsv E uart_cluster.bsv ● E Soc.defines Z Settings                                                         |  |

|-----------|-----------------------------------------------------------------------------------------------------------------|--|

|           | ster.bsv > {} uart_cluster > +0 Ifc_uart_cluster                                                                |  |

| 31        | package uart_cluster; $y$ arto An $(A_{A}, (A_{A}, A_{A}))$ $(A_{A}, (A_{A}, A_{A}))$ $(A_{A}, (A_{A}, A_{A}))$ |  |

| 41        | <pre>function Bit#(TLog#(`UARTCluster_Num_Slaves)) fn_slave_map (Bit#(`paddr) addr);</pre>                      |  |

| 55        | return slave_num;                                                                                               |  |

| 56        | endfunction:fn_slave_map                                                                                        |  |

| 57        |                                                                                                                 |  |

| 58        | <pre>interface Ifc_uart_cluster;</pre>                                                                          |  |

| 59        | interface RS232 uart0_io;                                                                                       |  |

| 60        | interface RS232 uart1_io;                                                                                       |  |

| 61        | <pre>interface RS232 uart2_io;</pre>                                                                            |  |

| 62        | <pre>interface.RS232.uart3_io;</pre>                                                                            |  |

| 63        | <pre>interface AXI4_Lite_Slave_IFC#(`paddr, 32, 0) slave;</pre>                                                 |  |

| 64        | <pre>method Bit#(3) uart_interrupts;</pre>                                                                      |  |

| 65        | endinterface                                                                                                    |  |

| 66        |                                                                                                                 |  |

| 67        | (*synthesize*)                                                                                                  |  |

| 68        | <pre>module mkuart(Ifc_uart_axi4lite#(32, 32, 0, 16));</pre>                                                    |  |

| 69        | <pre>let core_clock&lt;-exposeCurrentClock;</pre>                                                               |  |

| 70        | <pre>let core_reset&lt;-exposeCurrentReset;</pre>                                                               |  |

| 71        | <pre>let ifc();</pre>                                                                                           |  |

| 72        | <pre>mkuart_axi4lite#(core_clock, core_reset, 163, 0, 0) _temp(ifc);</pre>                                      |  |

| 73        | return ifc;                                                                                                     |  |

| 74        | endmodule                                                                                                       |  |

| 75        |                                                                                                                 |  |

| 76        |                                                                                                                 |  |

| 77        | <pre>module mkuart_cluster(Ifc_uart_cluster);</pre>                                                             |  |

| 78        | <pre>let curr_clk&lt;- exposeCurrentClock;</pre>                                                                |  |

| 79        | let curr_reset <- exposeCurrentReset;                                                                           |  |

| 80        | AXI4_Lite_Master_Xactor_IFC #(`paddr, 32, 0) c2m_xactor <- mkAXI4_Lite_Master_Xactor;                           |  |

| 81        | AXI4_Lite_Slave_Xactor_IFC #(`paddr, 32, 0) c2s_xactor <- mkAXI4_Lite_Slave_Xactor;                             |  |

| 82        | AXI4_Lite_Fabric_IFC #(`UARTCluster_Num_Masters, `UARTCluster_Num_Slaves, `paddr, 32,                           |  |

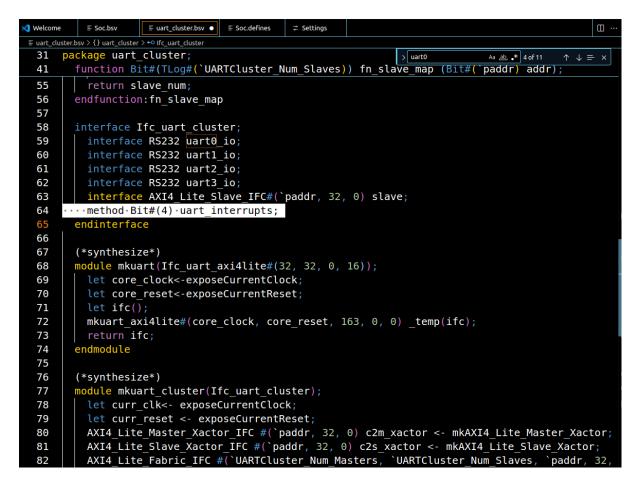

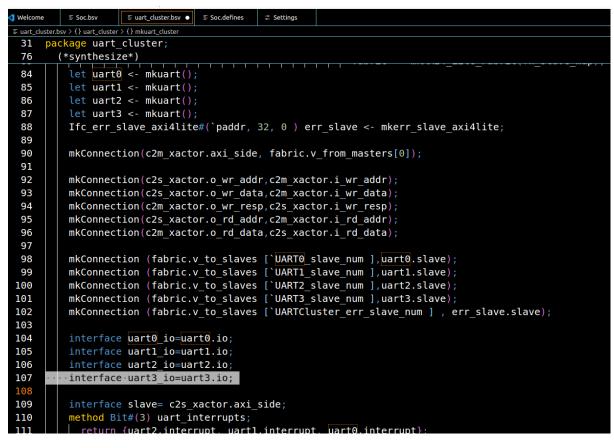

#### Step 3 (Add one more bit to take interrupt to Soc.bsv):

Add one more bit for the new UART Interrupt i.e. change the code from **Bit#(3)**

| 🗙 Welcome |                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------|

|           | ister.bsv > {} uart_cluster > +0 Ifc_uart_cluster                                                     |

|           | package uart_cluster;<br>$\downarrow$ uart0 Aa $\frac{ab}{4}$ * 4of 11 $\uparrow \downarrow \equiv x$ |

| 41        | <pre>function Bit#(TLog#(`UARTCluster_Num_Slaves)) fn_slave_map (Bit#(`paddr) addr);</pre>            |

| 55        | return slave_num;                                                                                     |

| 56        | endfunction:fn_slave_map                                                                              |

| 57        |                                                                                                       |

| 58        | interface Ifc_uart_cluster;                                                                           |

| 59        | <pre>interface RS232 uart0_io;</pre>                                                                  |

| 60        | <pre>interface RS232 uart1_io;</pre>                                                                  |

| 61        | <pre>interface RS232 uart2_io;</pre>                                                                  |

| 62        | <pre>interface RS232 uart3_io;</pre>                                                                  |

| 63        | <pre>interface AXI4_Lite_Slave_IFC#(`paddr, 32, 0) slave;</pre>                                       |

| 64        | <pre>method.Bit#(3).uart_interrupts;</pre>                                                            |

| 65        | endinterface                                                                                          |

| 66        |                                                                                                       |

| 67        | (*synthesize*)                                                                                        |

| 68        | <pre>module mkuart(Ifc_uart_axi4lite#(32, 32, 0, 16));</pre>                                          |

| 69        | <pre>let core_clock&lt;-exposeCurrentClock;</pre>                                                     |

| 70        | <pre>let core_reset&lt;-exposeCurrentReset;</pre>                                                     |

| 71        | <pre>let ifc();</pre>                                                                                 |

| 72        | <pre>mkuart_axi4lite#(core_clock, core_reset, 163, 0, 0) _temp(ifc);</pre>                            |

| 73        | return ifc;                                                                                           |

| 74<br>75  | endmodule                                                                                             |

| 75        | (*synthesize*)                                                                                        |

| 78        | <pre>module mkuart cluster(Ifc uart cluster);</pre>                                                   |

| 78        | let curr clk<- exposeCurrentClock;                                                                    |

| 78        | let curr reset <- exposeCurrentReset;                                                                 |

| 80        | AXI4_Lite_Master_Xactor_IFC #(`paddr, 32, 0) c2m_xactor <- mkAXI4_Lite_Master_Xactor;                 |

| 81        | AXI4_Lite_Master_Aactor_IfC #(`paddr, 32, 0) c2m_Aactor <- mkAXI4_Lite_Master_Aactor;                 |

| 82        | AXI4_Lite Fabric IFC #(`UARTCluster Num Masters, `UARTCluster Num Slaves, `paddr, 32,                 |

| 02        |                                                                                                       |

**to** Bit#(4)

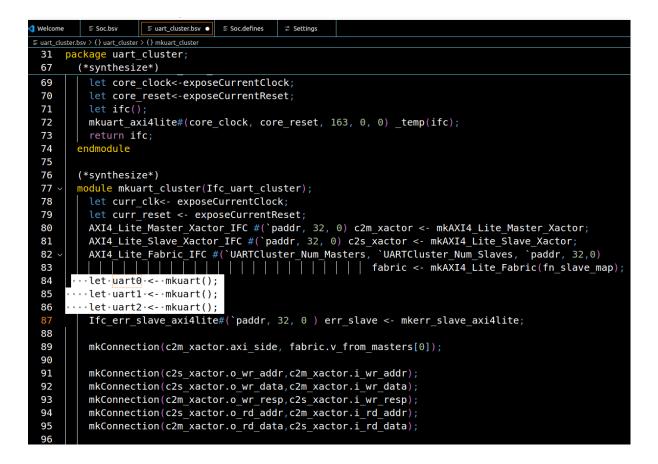

**Setp 4** (Add a UART module instance by assigning it to a new interface instance): Add one more instance for the UART interface i.e. change the code from

| Welcome    |                                                                                          |  |  |  |

|------------|------------------------------------------------------------------------------------------|--|--|--|

| ≣ uart_clu | ster.bsv > () uart_cluster > () mkuart_cluster                                           |  |  |  |

| 31         | 31 package uart_cluster;                                                                 |  |  |  |

| 67         | (*synthesize*)                                                                           |  |  |  |

| 69         | <pre>let core clock&lt;-exposeCurrentClock;</pre>                                        |  |  |  |

| 70         | <pre>let core_reset&lt;-exposeCurrentReset;</pre>                                        |  |  |  |

| 71         | <pre>let ifc();</pre>                                                                    |  |  |  |

| 72         | <pre>mkuart_axi4lite#(core_clock, core_reset, 163, 0, 0) _temp(ifc);</pre>               |  |  |  |

| 73         | return ifc;                                                                              |  |  |  |

| 74         | endmodule                                                                                |  |  |  |

| 75         |                                                                                          |  |  |  |

| 76         | (*synthesize*)                                                                           |  |  |  |

| 77         | <pre>module mkuart_cluster(Ifc_uart_cluster);</pre>                                      |  |  |  |

| 78         | <pre>let curr_clk&lt;- exposeCurrentClock;</pre>                                         |  |  |  |

| 79         | <pre>let curr_reset &lt;- exposeCurrentReset;</pre>                                      |  |  |  |

| 80         | AXI4_Lite_Master_Xactor_IFC #(`paddr, 32, 0) c2m_xactor <- mkAXI4_Lite_Master_Xactor;    |  |  |  |

| 81         | AXI4_Lite_Slave_Xactor_IFC #(`paddr, 32, 0) c2s_xactor <- mkAXI4_Lite_Slave_Xactor;      |  |  |  |

| 82         |                                                                                          |  |  |  |

| 83         | 3                                                                                        |  |  |  |

| 84         | <pre>let uart0 &lt;- mkuart();</pre>                                                     |  |  |  |

| 85         | <pre>let uart1 &lt;- mkuart();</pre>                                                     |  |  |  |

| 86         | <pre>let uart2 &lt;- mkuart();</pre>                                                     |  |  |  |

| 87         | <pre>let.uart3.<mkuart();< pre=""></mkuart();<></pre>                                    |  |  |  |

| 88         | <pre>Ifc_err_slave_axi4lite#(`paddr, 32, 0 ) err_slave &lt;- mkerr_slave_axi4lite;</pre> |  |  |  |

| 89         |                                                                                          |  |  |  |

| 90         | <pre>mkConnection(c2m_xactor.axi_side, fabric.v_from_masters[0]);</pre>                  |  |  |  |

| 91         |                                                                                          |  |  |  |

| 92         | <pre>mkConnection(c2s_xactor.o_wr_addr,c2m_xactor.i_wr_addr);</pre>                      |  |  |  |

| 93         | <pre>mkConnection(c2s_xactor.o_wr_data,c2m_xactor.i_wr_data);</pre>                      |  |  |  |

| 94         | <pre>mkConnection(c2m_xactor.o_wr_resp,c2s_xactor.i_wr_resp);</pre>                      |  |  |  |

| 95         | <pre>mkConnection(c2s_xactor.o_rd_addr,c2m_xactor.i_rd_addr);</pre>                      |  |  |  |

| 96         | <pre>mkConnection(c2m xactor.o rd data,c2s xactor.i rd data);</pre>                      |  |  |  |

|            |                                                                                          |  |  |  |

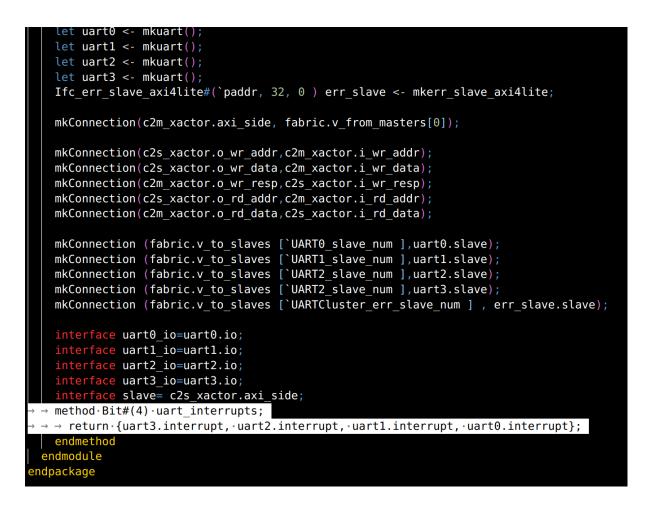

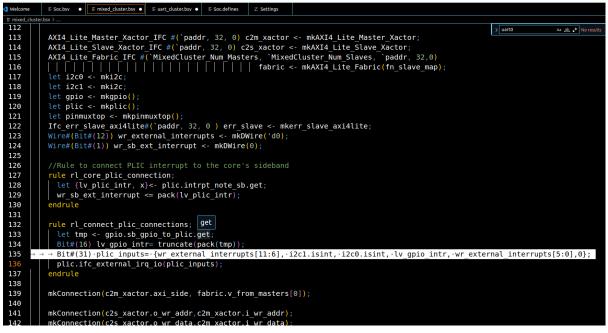

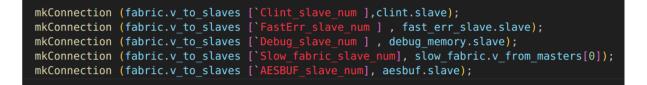

#### Step 5 (Connect the AXI4 interface with new UART):

Make a connection to the AXI4 interface i.e. Change the code from

```

≣ uart_cluster.bsv ● ≡ Soc.defines ≠ Settings

🜖 Welcome

≣ Soc.bsv

≡ uart_cluster.bsv > { } uart_cluster > { } mkuart_clust

31 package uart_cluster;

76

(*synthesize*)

let uart0 <- mkuart();</pre>

84

85

let uart1 <- mkuart();</pre>

let uart2 <- mkuart();</pre>

86

87

let uart3 <- mkuart();</pre>

Ifc_err_slave_axi4lite#(`paddr, 32, 0 ) err_slave <- mkerr_slave_axi4lite;</pre>

88

89

mkConnection(c2m_xactor.axi_side, fabric.v_from_masters[0]);

90

91

92

mkConnection(c2s_xactor.o_wr_addr,c2m_xactor.i_wr_addr);

mkConnection(c2s_xactor.o_wr_data,c2m_xactor.i_wr_data);

mkConnection(c2m_xactor.o_wr_resp,c2s_xactor.i_wr_resp);

93

94

mkConnection(c2s_xactor.o_rd_addr,c2m_xactor.i_rd_addr);

95

96

mkConnection(c2m_xactor.o_rd_data,c2s_xactor.i_rd_data);

97

98

mkConnection (fabric.v_to_slaves [`UART0_slave_num ],uart0.slave);

mkConnection (fabric.v to slaves [`UART1_slave_num ],uart1.slave);

99

mkConnection (fabric.v_to_slaves [`UART2_slave_num ],uart2.slave);

100

101

.→..mkConnection.(fabric.v_to_slaves.[`UART3_slave_num.],uart3.slave);

102

mkConnection (fabric.v to slaves [`UARTCluster err slave num ] , err slave.slave);

103

104

interface uart0_io=uart0.io;

105

interface uart1_io=uart1.io;

106

interface uart2_io=uart2.io;

interface slave= c2s_xactor.axi_side;

107

108

method Bit#(3) uart interrupts;

109

return {uart2.interrupt, uart1.interrupt, uart0.interrupt};

110

//return {uart2.interrupt, uart1.interrupt, uart0.interrupt};

ethod

```

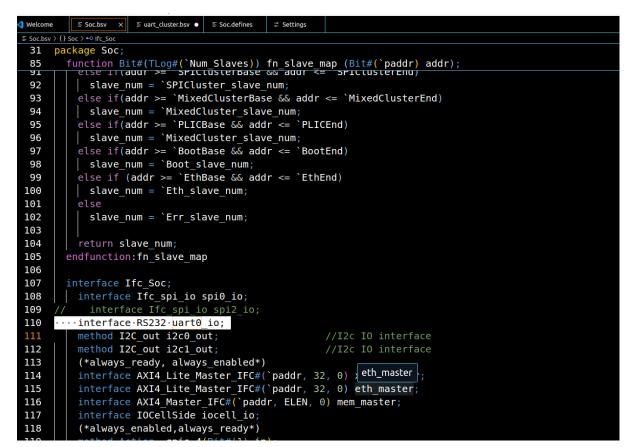

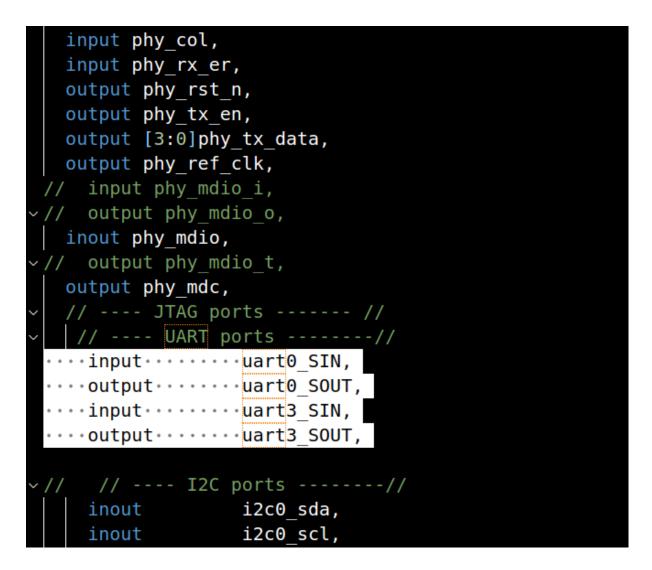

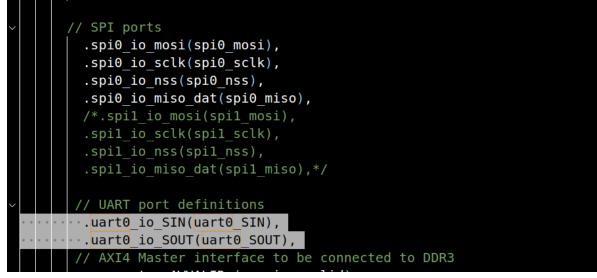

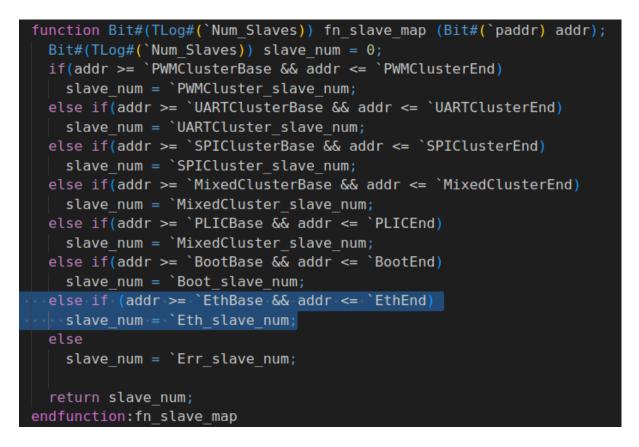

Step 6 (Add a new UART interface instance to take the UART interface from uart cluster into fpga\_top.v):

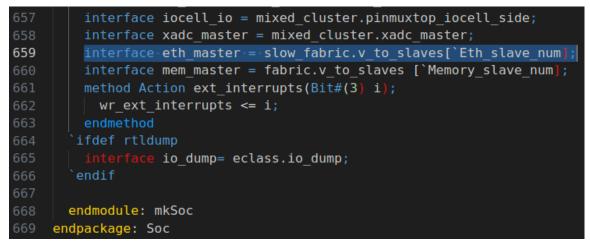

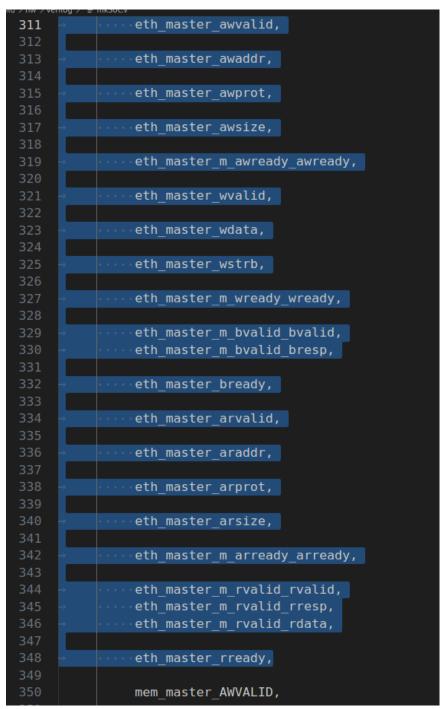

Add a new UART interface to soc.bsv by adding the following i.e. change the code from

| Welcome                                                     | E Soc.bsv E uart_cluster.bsv ● E Soc.defines                                                  |  |  |  |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| ≡ uart_cluster                                              | .bsv > () uart_cluster > () mkuart_cluster                                                    |  |  |  |

| 31 pa                                                       | ackage uart_cluster;                                                                          |  |  |  |

| 76                                                          | (*synthesize*)                                                                                |  |  |  |

| 84                                                          | let uart0 <- mkuart();                                                                        |  |  |  |

| 85                                                          | <pre>let uart1 &lt;- mkuart();</pre>                                                          |  |  |  |

| 86                                                          |                                                                                               |  |  |  |

| 87                                                          | let uart3 <- mkuart();                                                                        |  |  |  |

| 88                                                          | <pre>Ifc_err_slave_axi4lite#(`paddr, 32, 0 ) err_slave &lt;- mkerr_slave_axi4lite;</pre>      |  |  |  |

| 89                                                          |                                                                                               |  |  |  |

| 90                                                          | <pre>mkConnection(c2m_xactor.axi_side, fabric.v_from_masters[0]);</pre>                       |  |  |  |

| 91                                                          |                                                                                               |  |  |  |

| 92                                                          | <pre>mkConnection(c2s_xactor.o_wr_addr,c2m_xactor.i_wr_addr);</pre>                           |  |  |  |

| 93                                                          |                                                                                               |  |  |  |

| 94                                                          |                                                                                               |  |  |  |

| 95 mkConnection(c2s xactor.o rd addr,c2m xactor.i rd addr); |                                                                                               |  |  |  |

| 96 mkConnection(c2m_xactor.o_rd_data,c2s_xactor.i_rd_data); |                                                                                               |  |  |  |

| 97                                                          | 97                                                                                            |  |  |  |

| 98                                                          | <pre>mkConnection (fabric.v_to_slaves [`UART0_slave_num ],uart0.slave);</pre>                 |  |  |  |

| 99                                                          | <pre>mkConnection (fabric.v_to_slaves [`UART1_slave_num ],uart1.slave);</pre>                 |  |  |  |

| 100                                                         | <pre>mkConnection (fabric.v_to_slaves [`UART2_slave_num ],uart2.slave);</pre>                 |  |  |  |

| 101                                                         | <pre>mkConnection (fabric.v_to_slaves [`UART3_slave_num ],uart3.slave);</pre>                 |  |  |  |

| 102                                                         | <pre>mkConnection (fabric.v_to_slaves [`UARTCluster_err_slave_num ] , err_slave.slave);</pre> |  |  |  |

| 103                                                         |                                                                                               |  |  |  |

| 104 · ·                                                     | 104 ····interface·uart0_io=uart0.io;                                                          |  |  |  |

| 105 · ·                                                     | <pre>interface.uart1_io=uart1.io;</pre>                                                       |  |  |  |

| 106 · ·                                                     | <pre>interface.uart2_io=uart2.io;</pre>                                                       |  |  |  |

| 107                                                         | <pre>interface slave= c2s_xactor.axi_side;</pre>                                              |  |  |  |

| 108                                                         | <pre>method Bit#(3) uart_interrupts;</pre>                                                    |  |  |  |

| 109                                                         | <pre>return {uart2.interrupt, uart1.interrupt, uart0.interrupt};</pre>                        |  |  |  |